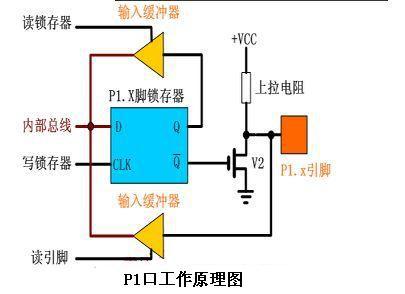

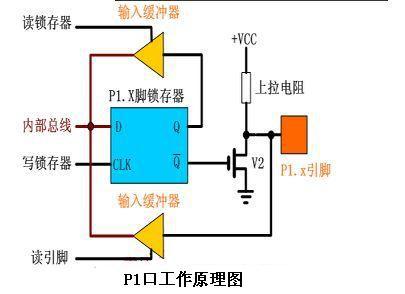

如果上拉電阻值過小,Vcc灌入端口的電流(Ic)將較大,這樣會(huì)導(dǎo)致MOS管V2(三極管)不完全導(dǎo)通(Ib*β,有飽和狀態(tài)變成放大狀態(tài),這樣端口輸出的低電平值增大(i2c協(xié)議規(guī)定���,端口輸出低電平的最高允許值為0.4v)。

如果上拉電阻過大����,加上線上的總線電容,由于RC影響�����,會(huì)帶來上升時(shí)間的增大(下降延是芯片內(nèi)的晶體管,是有源驅(qū)動(dòng)���,速度較快;上升延是無源的外接電阻�����,速度慢)��,而且上拉電阻過大�����,即引起輸出阻抗的增大��,當(dāng)輸出阻抗和負(fù)載的阻抗可以比擬的時(shí)���,則輸出的高電平會(huì)分壓而減少。

I2C的上拉電阻可以是1.5K�����,2.2K��,4.7K����, 電阻的大小對(duì)時(shí)序有一定影響,對(duì)信號(hào)的上升時(shí)間和下降時(shí)間也有影響��,一般接1.5K或2.2K�����。

(實(shí)驗(yàn):接入200K上拉電阻��,結(jié)果觀察到信號(hào)上升時(shí)間增大���,方波變成三角波)

I2C上拉電阻確定有一個(gè)計(jì)算公式:

Rmin={Vdd(min)-o.4V}/3mA

Rmax=(T/0.874) *c, T=1us 100KHz, T=0.3us 400KHz

C是Bus capacitanceRp最大值由總線最大容限(Cbmax)決定,Rp最小值由Vio與上拉驅(qū)動(dòng)電流(最大取3mA)決定;于是 Rpmin=5V/3mA≈1.7K(@Vio=5V)或者2.8V/3mA≈1K(@Vio=2.8V)����。

Rpmax的取值:100Kbps總線的負(fù)載最大容限<=400pF;快速模式�,400Kbps總線的負(fù)載最大容限<=200pF,根據(jù)具體使用情況、目前的器件制造工藝��、PCB的走線距離等因素以及標(biāo)準(zhǔn)的向下兼容性��,設(shè)計(jì)中以快速模式為基礎(chǔ)�����,即總線負(fù)載電容<200pF,也就是傳輸速度可以上到400Kbps是不成問題的����。于是Rpmax可以取的范圍是1.8K~7K @ Vio=5V對(duì)應(yīng)50pF~200pF根據(jù)Rpmin與Rpmax的限制范圍,一般取5.1K @ Vio=5V , 負(fù)載容限的環(huán)境要求也容易達(dá)到�。在2.8V系統(tǒng)中,console設(shè)計(jì)選3.3K,portable/handset等低供耗的設(shè)計(jì)選4.7K犧牲速度換取電池使用時(shí)間�。

總的來說:電源電壓限制了上拉電阻的最小值 ; 負(fù)載電容(總線電容)限制了上拉電阻的最大值。

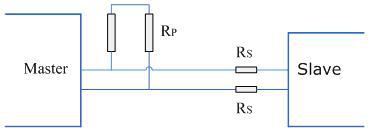

補(bǔ)充:在I2c總線可以串連300歐姆電阻RS可以用于防止SDA和SCL線的高電壓毛刺: I2c從設(shè)備的數(shù)量受總線電容,<=400pF的限制����。

上拉電阻阻值的確定

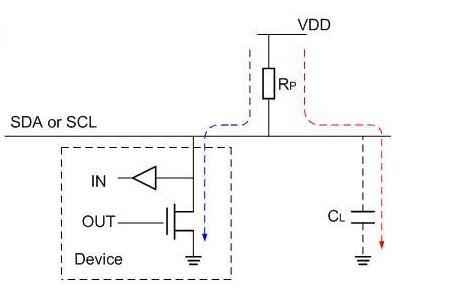

由于I2C接口采用OpenDrain機(jī)制,器件本身只能輸出低電平�,無法主動(dòng)輸出高電平,只能通過外部上拉電阻RP將信號(hào)線拉至高電平����。因此I2C總線上的上拉電阻是必須的!

RP不宜過小,一般不低于1KΩ

一般IO 端口的驅(qū)動(dòng)能力在2mA~4mA量級(jí)����。如果RP阻值過小,VDD灌入端口的電流將較大���,這樣會(huì)導(dǎo)致MOS管不完全導(dǎo)通���,有飽和狀態(tài)變成放大狀態(tài)���,這樣端口輸出的低電平值增大(I2C協(xié)議規(guī)定����,端口輸出低電平的最高允許值為0.4V);如果灌入端口的電流過大,還可能損壞端口�。故通常上拉電阻應(yīng)選取不低于1KΩ的電阻(當(dāng)VDD=3V時(shí),灌入電流不超過3mA)�。

RP不宜過大,一般不高于10KΩ

由于端口輸出高電平是通過RP實(shí)現(xiàn)的�,線上電平從低到高變化時(shí),電源通過RP對(duì)線上負(fù)載電容CL充電�����,這需要一定的時(shí)間��,即上升時(shí)間���。端口信號(hào)的上升時(shí)間可近似用充電時(shí)間常數(shù)RPCL乘積表示�。

信號(hào)線負(fù)載電容(對(duì)地)由多方面組成����,包括器件引腳��、PCB信號(hào)線����、連接器等���。如果信號(hào)線上掛有多個(gè)器件�,負(fù)載電容也會(huì)增大���。比如總線規(guī)定�,對(duì)于的400kbps速率應(yīng)用���,信號(hào)上升時(shí)間應(yīng)小于300ns;假設(shè)線上CL為20PF�,可計(jì)算出對(duì)應(yīng)的RP值為15KΩ�����。

如果RC充電時(shí)間常數(shù)過大��,將使得信號(hào)上升沿變化緩慢,達(dá)不到數(shù)據(jù)傳輸?shù)囊?��。因此一般?yīng)用中選取的都是幾KΩ量級(jí)的上拉電阻����,比如都選取4K7的電阻��。小阻值的RP電阻增大了端口Sink電流�,故在可能的情況下�,RP取值應(yīng)稍大一點(diǎn),以減少耗電�����。另外�,通產(chǎn)情況下,SDA,SCL兩條線上的上拉電阻取值是一致的����,并上拉到同一電源上。

PCB布局布線與抗干擾設(shè)計(jì)

I2C信號(hào)線屬于低速控制線�����,在手機(jī)PCB設(shè)計(jì)時(shí),按通常的控制IO對(duì)待即可����,無需做特別的保護(hù)設(shè)計(jì),一般不用擔(dān)心受到噪聲源干擾���。

但在一些特定的情況下���,比如折疊、滑蓋機(jī)型中���,I2C的兩根信號(hào)線需要通過轉(zhuǎn)軸或滑軌處的FPC���,此時(shí)由于信號(hào)路徑比較長(zhǎng),距離天線比較近���,而且Opendrain的輸出級(jí)對(duì)地阻抗大����,對(duì)干擾比較敏感��,因此比較容易受到RF信號(hào)源的干擾�����。在這種情況下,就應(yīng)適當(dāng)注意對(duì)I2C信號(hào)線的保護(hù)��。比如I2C兩條信號(hào)線(SDA,SCL)等長(zhǎng)度地平行走線��,兩邊加地線進(jìn)行保護(hù)��,避免臨近層出現(xiàn)高速信號(hào)線等��。

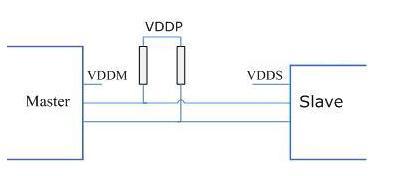

上拉電阻應(yīng)安置在OD輸出端附近�。當(dāng)I2C總線上主從器件(Master &

Slave)兩端均為OD輸出時(shí),電阻放置在信號(hào)路徑的中間位置�。當(dāng)主設(shè)備端是軟件模擬時(shí)序�,而從設(shè)備是OD輸出時(shí),應(yīng)將電阻安置在靠近從設(shè)備的位置����。

I2C協(xié)議還定義了串聯(lián)在SDA、SCL線上電阻Rs����。該電阻的作用是,有效抑制總線上的干擾脈沖進(jìn)入從設(shè)備�����,提高可靠性。這個(gè)電阻的選擇一般在100~200ohm左右�����。當(dāng)然,這個(gè)電阻并不是必須的����,在惡劣噪聲環(huán)境中,可以選用�。

比如常用的FM

接收模塊或者Capsense觸摸感應(yīng)功能塊,都是通過I2C接口控制的����。I2C接口信號(hào)從處理器出發(fā),經(jīng)過PCB上的信號(hào)路徑��,進(jìn)入上述電路單元�。I2C信號(hào)線上載有一定干擾,這種干擾雖然幅度并不很大�����,但還是會(huì)影響敏感的FM接收模塊或Capsense觸摸感應(yīng)功能塊���。此時(shí)��,可以通過在靠近FM模塊或觸摸感應(yīng)模塊的I2C信號(hào)線上串接Rs電阻��,即可有效降低干擾的影響�。此外,上拉電阻端的電源也要進(jìn)行退耦處理�����。

軟件模擬I2C時(shí)序

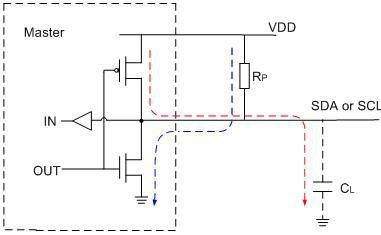

由于一般的I2C應(yīng)用速率并不高(400kbps)�����,使用處理器的IO口模擬I2C波形,完全可以勝任(處理器一般擔(dān)任Master�,占有I2C通信的控制權(quán),無需擔(dān)心隨機(jī)的I2C通信服務(wù)中斷其他任務(wù)的執(zhí)行)�。

處理器分配給I2C任務(wù)的IO口��,要求可以輸出高低電平����,還能配置為輸入端口。處理器根據(jù)總線規(guī)范以及從設(shè)備的時(shí)序要求�����,利用2條IO信號(hào)線,模擬I2C接口時(shí)序波形����,進(jìn)行I2C通信。

處理器發(fā)送數(shù)據(jù)時(shí)����,通過IO口輸出高電平,上升時(shí)間基本與外部上來電阻阻值無關(guān)���,且比用外部上拉電阻上拉到高電平快很多�。處理器在接受數(shù)據(jù)時(shí)��,即便上拉電阻阻值選的大一些���,從設(shè)備輸出數(shù)據(jù)的波形上升沿緩慢�,但由于處理器使用軟件采樣的而非硬件采樣����,因此,對(duì)數(shù)據(jù)傳輸?shù)慕Y(jié)果并不影響��。也就是說,使用IO口模擬I2C時(shí)序時(shí)�,上拉電阻阻值可以適當(dāng)選的大一些。

需要指出的是����,使用軟件模擬最多只能完成單Master的應(yīng)用,對(duì)于多Master應(yīng)用���,由于需要進(jìn)行總線控制權(quán)的仲裁管理�����,使用軟件模擬的方法很難完成��。

I2C總線空閑的時(shí)候�,兩條信號(hào)線應(yīng)該維持高電平�。否則,上拉電阻上會(huì)有耗電���。特別是在上電過程中�,IO線上電平也應(yīng)保持在高電平狀態(tài)�����。也就是說:當(dāng)Master的I2C使用的是IO軟件模擬時(shí)����,一定要保證該兩個(gè)IO上電默認(rèn)均為輸入(或高阻)或者輸出高電平,切不可默認(rèn)為輸出低電平�。IO默認(rèn)為輸入時(shí),可以通過外部上拉電阻將I2C信號(hào)線拉至高電平����。

I2C應(yīng)用中上拉電阻電源問題

在部中分應(yīng)用中,還存在主從設(shè)備以及上拉電阻電源不一致的情況���,比如Camera模組���。在很多設(shè)計(jì)方案中,Camera模組不工作時(shí)����,并不是進(jìn)入PowerDown模式,而是直接關(guān)閉模組供電VDDS�。此時(shí),處理器與模組相互連接的所有信號(hào)線都應(yīng)該進(jìn)入高阻態(tài)�����,否則就會(huì)有電流漏入模組;而對(duì)于此時(shí)的I2C控制信號(hào)線來說,由于上拉電阻的存在��,必須關(guān)斷上拉電阻電源VDDP��。如果上拉電阻使用的是系統(tǒng)電源VDDM(VDDP=VDDM)�,無法關(guān)閉,就會(huì)有漏電流進(jìn)入模組;因此這種情況下��,應(yīng)該使用VDDS作為上拉電阻電源(VDDP=VDDS)��,這樣上拉電阻電源與Slave電源即可同時(shí)關(guān)閉,切斷了漏電路徑�。

另外需要注意的是,在上述應(yīng)用實(shí)例中選擇的IO��,應(yīng)該選取上電默認(rèn)為輸入(或高阻)才行���。

--------------------------------------------------------------------------------------------------------------------

附錄 上拉電阻

上拉就是將不確定的信號(hào)通過一個(gè)電阻鉗位在高電平�,電阻同時(shí)起限流作用��。下拉同理��,也是將不確定的信號(hào)通過一個(gè)電阻鉗位在低電平�����。

上拉是對(duì)器件輸入電流�����,下拉是輸出電流����;強(qiáng)弱只是上拉電阻的阻值不同,沒有什么嚴(yán)格區(qū)分����;對(duì)于非集電極(或漏極)開路輸出型電路(如普通門電路)提供電流和電壓的能力是有限的,上拉電阻的功能主要是為集電極開路輸出型電路輸出電流通道��。

作用

1���、當(dāng)TTL電路驅(qū)動(dòng)CMOS電路時(shí)���,如果電路輸出的高電平低于CMOS電路的最低高電平(一般為3.5V), 這時(shí)就需要在TTL的輸出端接上拉電阻���,以提高輸出高電平的值�。

2、OC門電路必須使用上拉電阻�,以提高輸出的高電平值。

3���、為增強(qiáng)輸出引腳的驅(qū)動(dòng)能力�,有的單片機(jī)管腳上也常使用上拉電阻�。

4、在CMOS芯片上�����,為了防止靜電造成損壞�,不用的管腳不能懸空,一般接上拉電阻以降低輸入阻抗��, 提供泄荷通路�。

5、芯片的管腳加上拉電阻來提高輸出電平���,從而提高芯片輸入信號(hào)的噪聲容限�����,增強(qiáng)抗干擾能力�����。

6���、提高總線的抗電磁干擾能力����,管腳懸空就比較容易接受外界的電磁干擾��。

7�、長(zhǎng)線傳輸中電阻不匹配容易引起反射波干擾�,加上、下拉電阻是電阻匹配�,有效的抑制反射波干擾。

概念

就是從電源高電平引出的電阻接到輸出端

1���,如果電平用OC(集電極開路���,TTL)或OD(漏極開路,CMOS)輸出��,那么不用上拉電阻是不能工作的���, 這個(gè)很容易理解�����,管子沒有電源就不能輸出高電平了����。

2,如果輸出電流比較大��,輸出的電平就會(huì)降低(電路中已經(jīng)有了一個(gè)上拉電阻�����,但是電阻太大����,壓降太高),就可以用上拉電阻提供電流分量�����, 把電平“拉高”��。(就是并一個(gè)電阻在IC內(nèi)部的上拉電阻上�����,這時(shí)總電阻減小,總電流增大)��。當(dāng)然管子按需要工作在線性范圍的上拉電阻不能太小���。當(dāng)然也會(huì)用這個(gè)方式來實(shí)現(xiàn)門電路電平的匹配����。

注意事項(xiàng)

需要注意的是����,上拉電阻太大會(huì)引起輸出電平的延遲�����。(RC延時(shí))

一般CMOS門電路輸出不能給它懸空��,都是接上拉電阻設(shè)定成高電平�。

下拉電阻:和上拉電阻的原理差不多, 只是拉到GND去而已�。 那樣電平就會(huì)被拉低。 下拉電阻一般用于設(shè)定低電平或者是阻抗匹配(抗回波干擾)����。

上拉電阻阻值的選擇原則包括:

1�、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大�;電阻大,電流小����。

2、從確保足夠的驅(qū)動(dòng)電流考慮應(yīng)當(dāng)足夠?�?�;電阻小��,電流大���。

3�、對(duì)于高速電路���,過大的上拉電阻可能邊沿變平緩�。綜合考慮

以上三點(diǎn),通常在1k到10k之間選取��。對(duì)下拉電阻也有類似道理�。

使用原因

一般作單鍵觸發(fā)使用時(shí)���,如果IC本身沒有內(nèi)接電阻,為了使單鍵維持在不被觸發(fā)的狀態(tài)或是觸發(fā)后回到原狀態(tài)���,必須在IC外部另接一電阻���。

數(shù)字電路有三種狀態(tài):高電平、低電平�、和高阻狀態(tài),有些應(yīng)用場(chǎng)合不希望出現(xiàn)高阻狀態(tài)�����,可以通過上拉電阻或下拉電阻的方式使處于穩(wěn)定狀態(tài)����,具體視設(shè)計(jì)要求而定����!

一般說的是I/O端口,有的可以設(shè)置��,有的不可以設(shè)置����,有的是內(nèi)置�,有的是需要外接����,I/O端口的輸出類似于一個(gè)三極管的C,當(dāng)C接通過一個(gè)電阻和電源連接在一起的時(shí)候���,該電阻成為上拉電阻�,也就是說��,該端口正常時(shí)為高電平���;C通過一個(gè)電阻和地連接在一起的時(shí)候�,該電阻稱為下拉電阻��。

上拉電阻是用來解決總線驅(qū)動(dòng)能力不足時(shí)提供電流的問題的�����。一般說法是上拉增大電流�����,下拉電阻是用來吸收電流。

產(chǎn)品中心

產(chǎn)品中心

選型指南

選型指南

文庫&下載

文庫&下載

在線視頻

在線視頻

服務(wù)中心

服務(wù)中心

案例分享

案例分享

新聞中心

新聞中心

關(guān)于我們

關(guān)于我們

聯(lián)系我們

聯(lián)系我們